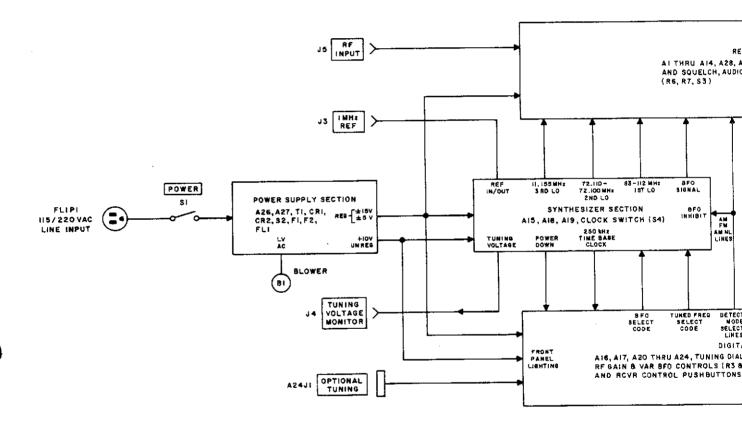

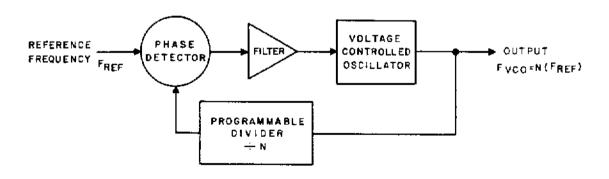

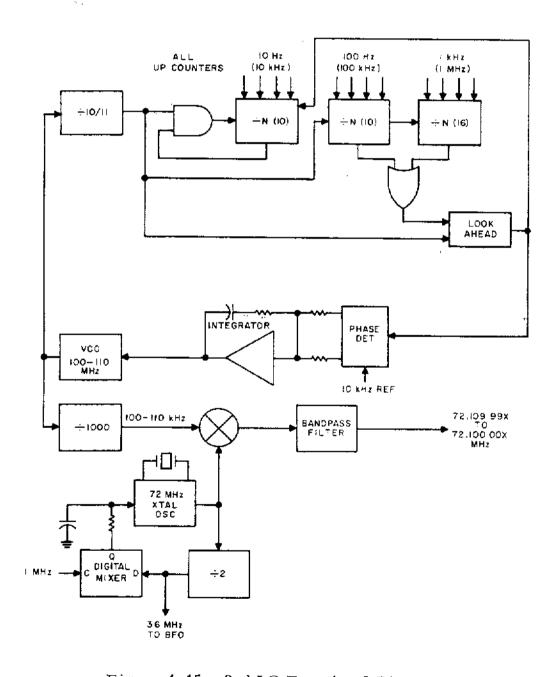

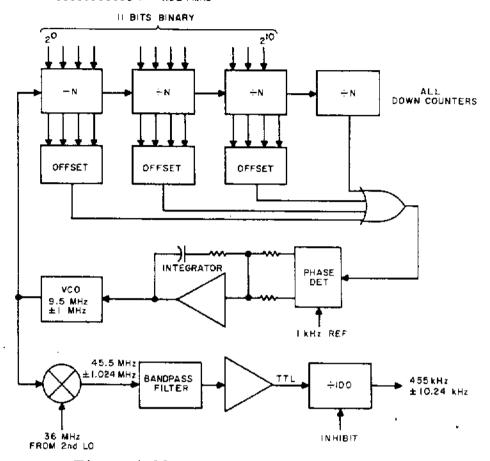

Figure 4-1. WJ-8888, Simplified Overall Block Diagram

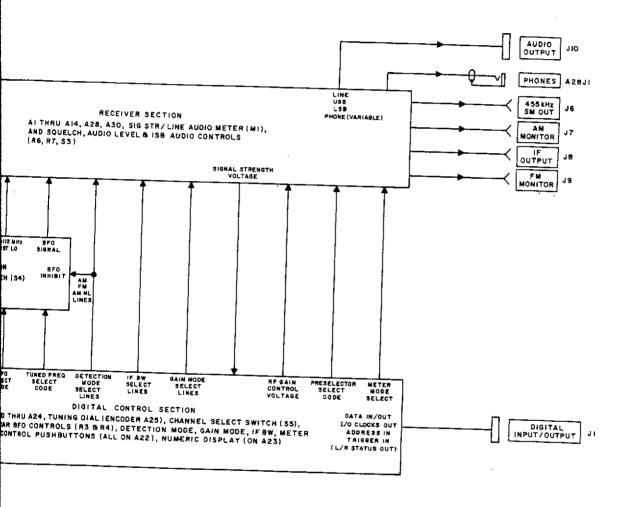

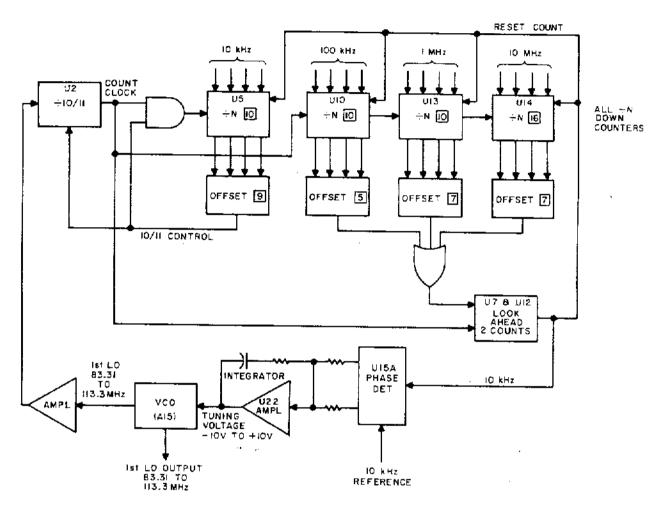

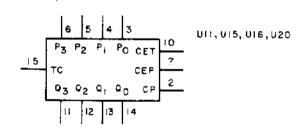

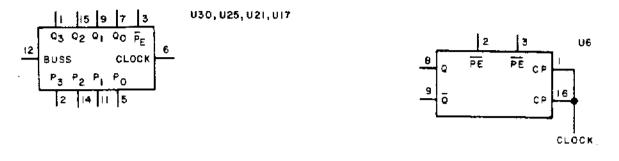

Figure 4-2. Receiver Section, Simplified Functional Block Diagram

# SECTION IV CIRCUIT DESCRIPTION

### 4.1 GENERAL

The following paragraphs describe the various circuits of the WJ-8888 Receiver. The receiver is, for purposes of description, divided into four functional sections, these being the receiver section, synthesizer section, digital control section, and the power supply section. An overall simplified functional description preceeds detailed descriptions of the four functional sections. The discussions of the receiver, synthesizer, digital control, and power supply sections consist of schematic descriptions introduced by more detailed functional discussions of these sections. Functional block diagrams are included where required. The schematic descriptions are arranged in functional sequence rather than in numerical sequence to facilitate progressive reading. The table of contents of this manual should be consulted for locating descriptions of specific circuits. It is assumed that the reader of this section is familiar with the preceding sections of this manual.

In this instrument, the unit numbering system is used for identification of electrical components, such that each circuit-board or assembly part carries a prefix before the usual class letter and item number. For example, the full designation for R1 on circuit board A4 is A4R1. These prefixes are omitted on illustrations and in the text except where they are necessary to avoid confusion.

### 4.2 OVERALL FUNCTIONAL DESCRIPTION

The simplified overall diagram, Figure 4-1, shows the relationship between the four major functional sections of the WJ-8888. The blocks shown on the drawing list subassemblies and controls falling into each functional category, permitting the main chassis schematic, Figure 7-33, to be keyed to this diagram.

The receiver section tunes to a selected center frequency in the 0.5 to 30.5 MHz range from the RF input connector (antenna input). The signal may be AM, FM, pulsed CW, SSB (USB or LSB), or ISB (independent sideband). The signal is demodulated as required to produce an audio output. Wideband IF, predetection IF, and AM and FM monitor outputs are also provided by the receiver section.

Most of the operating parameters of the receiver section are controlled by the digital control section, including the tuned frequency and BFO frequency which are controlled indirectly via the synthesizer section. The specified receiver parameters controlled by the digital control section are shown on the block diagram. An analog signal strength voltage is returned from the receiver section to the digital control section where it is converted to binary code for inclusion in the data word (to be discussed in paragraph 4.5).

The tuned frequency and BFO select codes applied to the synthesizer section cause the synthesizer to provide appropriate first and second LO and BFO frequencies to the receiver section. The third LO frequency is fixed at 11.155 MHz. The BFO synthesizer output is disabled when the detection mode is AM, FM or AM NL. The proper receiver preselector is automatically selected as a

function of the tuned frequency. The digital control section obtains its time base clock from the synthesizer section. In addition, the power-down detector is located in the synthesizer section, although the main power-down latch circuit is located in the digital control section.

The specifications of the 1 MHz reference input/output, the tuning voltage monitor output, the optional tuning input, and the digital control input/output, the optional tuning output, and the digital control input/output, as well as the receiver section inputs and outputs and power requirements are described in detail in sections I and II of this manual.

### 4,3 RECEIVER SECTION

In this paragraph, the RF, IF, demodulation, and AF portions of the WJ-8888 Receiver are described. The discussion begins with a functional block diagram description, which is followed by a detailed circuit description based on the schematic diagrams. The circuit descriptions are arranged in functional rather than numerical sequence to facilitate progressive reading.

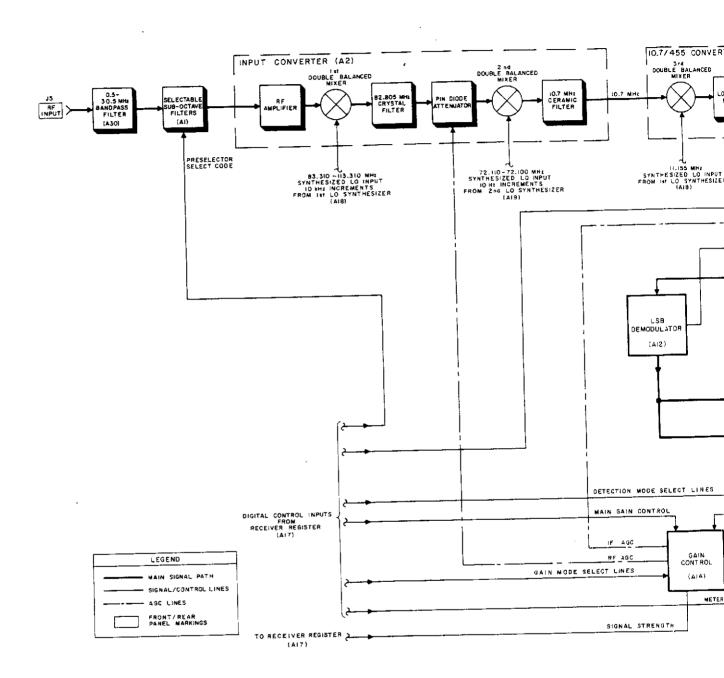

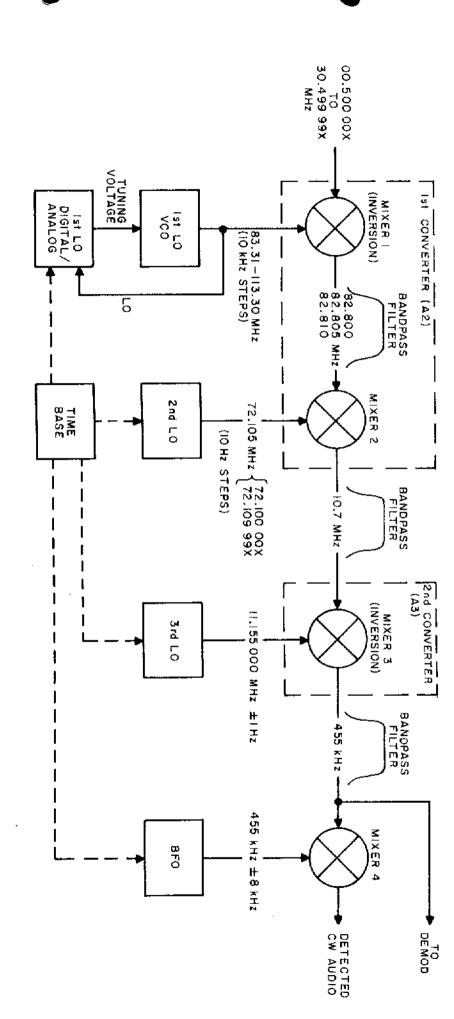

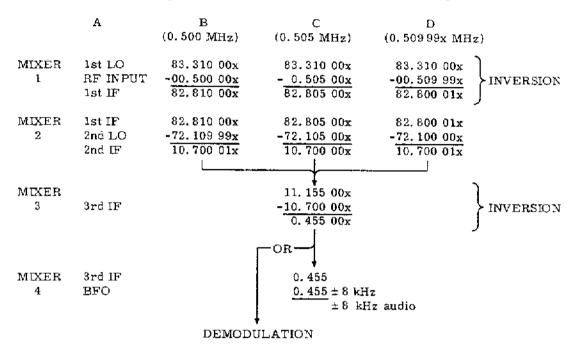

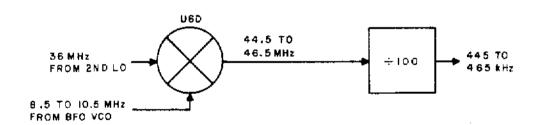

4.3.1 FUNCTIONAL BLOCK DIAGRAM DESCRIPTION. - Referring to functional block diagram Figure 4-2, the broadband signal from the receiving antenna is applied through J5 (RF INPUT) to a 0.5-30 MHz bandpass filter (A30). The filter output is applied to one of eight digitally selectable sub-octave filters (the term sub-octave filter refers to the fact that the passband extends over a less than 2-to-1 frequency range). Digital filter select data from the receiver register automatically selects the sub-octave filter appropriate for the frequency being tuned. The broadband nature of the input filters eliminates the need for variable-tuned RF circuitry, thus avoiding alignment and tracking difficulties. The output of the sub-octave filter is amplified by a grounded-gate JFET RF amplifier and then mixed in the first double-balanced mixer with a 83.310-113.310 MHz LO signal obtained from the synthesizer section. The 82.805 MHz difference frequency is used as the first IF.

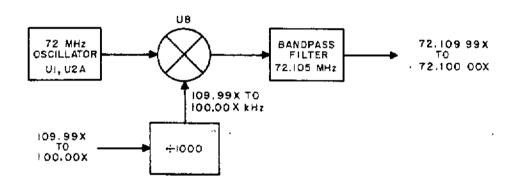

The mixer output is applied to a crystal filter which passes only the  $35~\mathrm{kHz}\text{-wide}$  difference-frequency band centered at 82.805 MHz. The 82.805 MHz IF signal is applied to a PIN diode attenuator which is controlled by the RF AGC voltage derived in the gain control section. A shaper circuit provides the desired After attenuation, the signal is mixed with a 72.110-RF AGC characteristic. 72.100 synthesized LO signal in the second double-balanced mixer to produce The 10.7 MHz ceramic filter passes only the sum and difference frequencies. 250 kHz-wide difference-frequency band centered at 10.7 MHz. This second IF is applied to the 10.7/455 converter (A3) where it is mixed in the third doublebalanced mixer with an 11.155 MHz fixed-frequency synthesized LO input to produce the final IF of 455 kHz. The low-pass filter after the mixer rejects mixer sum and feed-through products, permitting only the desired signals at or near 455 kHz to pass.

Tuning is accomplished by varying the frequencies of the synthesized LO inputs applied to the first and second double-balanced mixers. The LO input to the first mixer covers the 83.310-113.310 MHz range in discrete 10 kHz increments. For finer resolution, the LO input to the second mixer covers the

72.110-72.100 MHz range (a 10 kHz spread) in 10 Hz increments. As the operator tunes the receiver upward in frequency, the second LO frequency decreases from 72.110 MHz in 10 Hz increments until it reaches 72.100 MHz. At this point, the first LO frequency which was constant, automatically advances by one 10 kHz increment while the second LO frequency resets to 72.110 MHz and continues decreasing in 10 Hz increments as before as the operator continues tuning the receiver upward. If the operator tunes the receiver lower in frequency, the above process is reversed. In this manner the entire 0.5-30.5 MHz tuning range of the receiver is covered in 10 Hz increments without the need for band changing. To eliminate sideband inversions, it is necessary that the synthesized LO frequencies move in opposite directions during receiver tuning.

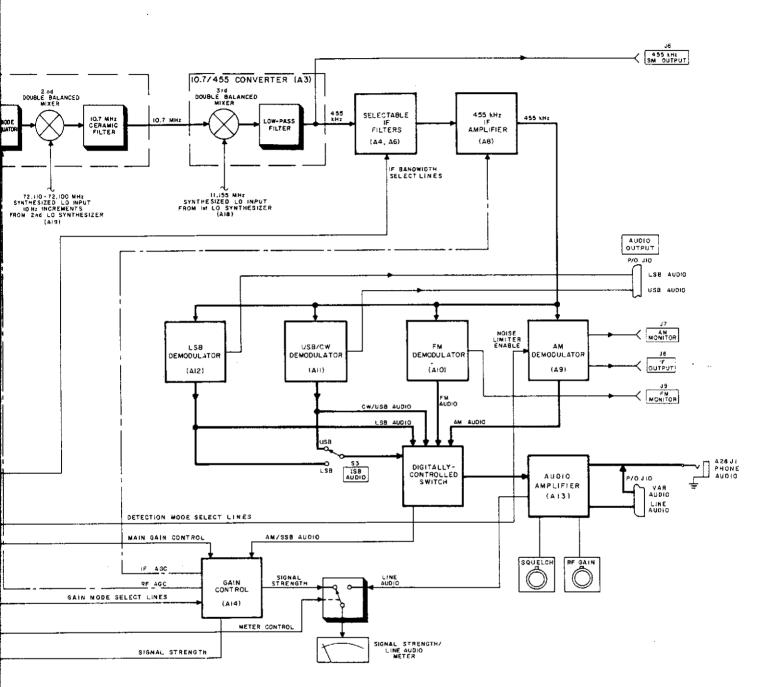

The output of the low-pass filter on the 10.7/455 converter (A3) is available as a 455 kHz signal monitor output for use with an external panoramic display unit. The 455 kHz signal is also applied to the input of one of six digitally-selectable IF filters. The four filters supplied with the receiver have 3 dB bandwidths of 0.5, 2.0, 4.0, and 8.0 kHz respectively; bandwidths of the remaining two filters (if desired) are determined by the user. After being amplified by the 455 kHz IF amplifier (A8), the IF signal is applied simultaneously to AM, FM, CW/USB and LSB demodulators.

The AM demodulator employs a full-wave diode envelope detector to recover the audio modulation from the carrier. A noise limiter circuit included in the AM demodulator can be activated to reduce impulse-type noise. The FM demodulator employs a symmetrical IC limiter and discriminator circuit. For CW/USB/ LSB demodulation, a 455 kHz variable or fixed BFO signal is combined with the IF signal in a product detector to produce a demodulated audio output. Separate demodulators are used for CW/USB and LSB detection.

All demodulator outputs are applied to a digitally-controlled switch, which routes the selected demodulator output signal to the audio amplifier (A13). The audio amplifier builds up the signal to a level sufficient to drive a pair of headphones and also provides a line audio output. The selected demodulator output from the digitally-controlled switch is also applied to the gain control circuit (A14) which uses this signal to produce the AGC voltage outputs applied to the RF and IF sections. Three gain control modes are available - normal AGC (fast-attack fast-decay), hold AGC (fast-attack delayed-decay), and manual gain control (receiver gain adjustable by the RF GAIN control on front panel). In the ISB detection mode, the receiver gain mode is automatically set to normal AGC while independent fast-attack slow-decay AGC loops in the SSB demodulators are activated. The front panel meter may indicate either the signal strength or audio level.

#### 4.3.2 SCHEMATIC DESCRIPTIONS.

4.3.2.1 Type 791312 0.5-30 MHz Bandpass Filter (A20). - Figure 7-32 is the schematic diagram for the 0.5-30 MHz bandpass filter. Signals from the antenna are applied to the five-pole filter through J1. The filter actually consists of a high-pass filter with a cut-off frequency just below 0.5 MHz in tandem with a low-pass filter with a cut-off frequency just above 30 MHz. The combined

responses of these filters result in the desired 0.5-30 MHz bandpass characteristic. Signals in the 0.5-30 MHz range leave the filter at J2, and are applied to the sub-octave preselector filters on the input filter assembly (A1).

Type 791199 Input Filter Assembly (A1). - Figure 7-1 is the schematic 4.3.2.2 diagram for the input filter assembly. Signals from J2 of the 0.5-30 MHz bandpass filter (A30) are applied to J1. The filter assembly mounts a mother board (A1) which in turn mounts four filter boards (A1A1, A1A2, A1A3, and A1A4). The RF input from J1 is applied to all four filter boards simultaneously. filter board contains two sub-octave filters. Diode switches at the input and output of each sub-octave filter are digitally controlled by a three bit binary word  $(2^0, 2^1, 2^2)$  at the control input from the receiver register board. integrated circuit on the 10-18/18-30 MHz filter board (A1A1) decodes the binary word and causes another integrated circuit on one of the four filter boards to forward bias the diode switches of the correct sub-octave filter, while holding the diode switches of the remaining sub-octave filters reverse biased so that no signals will pass through them. Thus, signals pass through only the correct suboctave filter.

10-18/18-30 MHz Filter (A1A1A1). - Figure 7-2 is the Type 791247 schematic diagram for the 10-18/18-30 MHz filter. Two elliptical function suboctave filters are contained on the board, each consisting of three low-pass sections followed by three high-pass sections. The RF signal output from the 0.5-30 MHz bandpass filter (A30) is applied simultaneously to both sub-octave filter inputs (as well as to the six sub-octave filter inputs on the other three boards). Diode switches at each filter input, however, prevent the RF signal from passing to all but the selected sub-octave filter. Assuming that the 18-30 MHz filter has been selected, pin 5 (2Y) of U1 is in the on state (at ground potential) resulting in electron flow from that point through R2 and L5. From L5, electrons flow to the +5 V supply source through two parallel branches. One of these branches comprises series circuit CR2, CR1, and L1. The other comprises series circuit CR5, L4, and R18. The resulting 80 mA of current through each diode results in a heavy forward bias which in turn permits the RF input to pass through diodes CR2 and CR5 to the filter (the heavy forward bias results in the high dynamic range of the diodes). L1, L4, and L5 are RF chokes which isolate the signal path from the dc control path. An identical diode switch at the filter output permits the RF signal to pass through C35 to the output of the filter board. The 10-18 MHz filter, however, is isolated from the RF input by the reverse bias on its switching diodes (CR3, CR4, CR6, CR9, CR10, and CR12). Since pin 3 (1Y) of U1 is in the off state, no current flows in or out of that terminal. As a result, the +15 V supply source reverse biases the diodes through R4, thus isolating the 10-18 MHz filter from the RF signal input and output. The remaining six sub-octave filters on the other filter boards are similarly switched out of the signal path. The diode switches are designed so that the series diodes (CR2, CR3, CR5, CR6, CR7, CR8, CR9, and CR10) perform the actual RF signal switching, while the shunt diodes (CR1, CR4, CR11, and CR12) prevent corresponding RF chokes L1, L2, L24, and L25 from interacting with other filter inputs. For

example if the 10-18 MHz filter is being used, the reverse bias on CR1 in the 18-30 MHz filter prevents RF choke L1 from effectively shunting the input of the 10-18 MHz filter. The Y outputs of one-of-eight decoder U1 are controlled by the corresponding A inputs (see Table 4-1). Since the B inputs are grounded, it is only necessary to ground the A inputs to turn on (ground) the Y outputs. The A inputs in turn are controlled by U2 outputs 0 and 1 (U2 outputs 2-7 perform the same function for the other three filter boards). U2 outputs 0-7 are controlled by a 3 bit binary word at control inputs A, B, and C (see Table 4-1). The digital word determines which one of U2's outputs (0-7) is low (all others are high). The single low output of U2 determines which Y output of U1 is grounded (turned on), and consequently, which sub-octave filter is selected. The control inputs to U8 come from the receiver register.

Type 791250 3.4-6.0/6.0-10 MHz Filter (A1A1A2). - Figure 7-3 is the schematic diagram for this filter board. It is functionally identical to the filter board described above. Some component values are different as a result of the different frequency coverage. Decoding of the digital word from the receiver register is done by A1A1A1U2 as previously described.

Type 791249 1.2-2.0/2.0-3.4 MHz Filter (A1A1A3) and Type 791248 0.5-0.8/0.8-1.2 MHz Filter (A1A1A4). - Figures 7-4 and 7-5 are the respective schematic diagrams for these filter boards. Since these filters are very similar to the ones described above, no further circuit discussion is required.

4.3.2.3 Type 79116 Input Converter (A2). - Figure 7-6 is the schematic diagram for the input converter. The signals from the input filter assembly (A1) are amplified and up-converted to the 82.805 MHz first IF. The 82.805 MHz IF is applied to a 35 kHz bandwidth filter and then amplified. The amplified bandlimited IF is then applied to a PIN diode attenuator controlled by the RF AGC voltage (shaped for the desired AGC characteristic by attenuator shaper A1). After another stage of amplification, the 82.805 MHz IF is down-converted to 10.7 MHz. The 10.7 MHz second IF leaves the input converter after passing through a 250 kHz bandwidth ceramic filter.

RF Amplifier. - Incoming signals at J1 are applied to the RF amplifier through a 32 MHz cut-off frequency low-pass filter composed of C10, C11, and L1. The low-pass filter reduces LO-to-antenna conduction and improves RF image rejection. Q2 is a common gate amplifier source-biased by constant current generator Q1. Diode CR1 minimizes Q1 collector current changes due to temperature by changing base bias on Q1 to counteract the normal change with temperature in Q1 collector current (a rise in temperature causes CR1 to develop a lower forward voltage drop, thus lowering the base bias of Q1 in the same proportion as Q1's base-emitter voltage, thereby maintaining a constant voltage across R4). Similarly, a reduction in temperature results in a higher base bias on Q1, thus compensating for the normal decrease with temperature in Q1 collector current. Thus, the operating point of Q1 (and therefore Q2) is stabilized over a wide temperature range. L4 and T1 comprise a broadband impedance matching network

Table 4-1. Truth Tables for Input Filter Logic Elements

SN75453P (U1)

| A | В | Y       |

|---|---|---------|

| 0 | 0 | 0 (ON)  |

| 0 | 1 | 1 (OFF) |

| 1 | 0 | 1 (OFF) |

| 1 | 1 | 1 (OFF) |

NOTE: "0" Indicates Ground Potential

"1" Indicates A Positive Potential

8250 (U2)

| INPUTS |       |                    | OUTPUTS* |   |   |   |   | FILTER |   |   |                  |

|--------|-------|--------------------|----------|---|---|---|---|--------|---|---|------------------|

| A(20)  | B(21) | C(2 <sup>2</sup> ) | 0        | 1 | 2 | 3 | 4 | 5      | 6 | 7 | FREQUENCY<br>MHz |

| 0      | 0     | 0                  | 0        | 1 | 1 | 1 | 1 | 1      | 1 | 1 | 18-30            |

| 1      | 0     | 0                  | 1        | 0 | 1 | 1 | 1 | 1      | 1 | 1 | 10-18            |

| 0      | 1     | 0                  | 1        | 1 | 0 | 1 | 1 | 1      | 1 | 1 | 6.0-10           |

| 1      | 1     | 0                  | 1        | 1 | 1 | 0 | 1 | 1      | 1 | 1 | 3.4-6.0          |

| 0      | 0     | 1                  | 1        | 1 | 1 | 1 | 0 | 1      | 1 | 1 | 2.0-3.4          |

| 1      | 0     | 1                  | 1        | 1 | 1 | 1 | 1 | 0      | 1 | 1 | 1.2-2.0          |

| 0      | 1     | 1                  | 1        | 1 | 1 | 1 | 1 | 1      | 0 | 1 | 0.8-1.2          |

| 1      | 1     | 1                  | 1        | 1 | 1 | 1 | 1 | 1      | 1 | 0 | 0.5-0.8          |

<sup>\*</sup>Designations for outputs do not correspond with IC pin numbers.

that is used to couple the output of Q2 to the lower impedance input of mixer U1. R1 functions as a parasitic suppressor, while R5 loads L2 to prevent resonant effects. R6 establishes the output impedance of Q2.

First Mixer, LO Amplifier. - Double-balanced mixer U1 combines the RF amplifier output with the 83.310-113.310 MHz LO input from LO amplifier A3Q2 to produce the 82.805 MHz first IF. 35 kHz bandwidth filter FL1 passes the difference frequencies while attenuating sum and other mixer products. L9-C23 and L10-C24 tune the filter input and output, respectively. The LO amplifier increases the amplitude of the 83.310-113.310 MHz synthesized LO input to the 27-30 dBm level required by double-balanced mixer U1. A3Q2 operates as a common emitter stage base-biased by A3Q1. A3CR1 stabilizes the base bias current into A3Q1 against temperature variations in much the same manner as CR1 stabilizes the operating points of Q1 and RF amplifier Q2 as described above. A3R4 and A3L1 introduce degenerative feedback that decreases with frequency resulting in a more uniform output level from A3Q2 over the 83.310-113.310 MHz frequency range. R20, R23, and C28 establish the input impedance of the stage.

82.805 MHz IF Amplifiers, PIN Diode Attenuator. - The output of FL1 is applied to common gate 82.805 MHz IF amplifier Q5. CR2 and Q4 provide temperature-stabilized source bias for Q5 in the same manner as CR1 and Q1 provide temperature-stabilized source bias for RF amplifier Q2. circuit consists of a parallel resonant tank provided by the shunt combination of C30 and C31 effectively in parallel with T2 (one end of T2 is grounded by C29). A tap on T2 matches the high impedance output of Q5 to the low impedance present at the PIN diode attenuator input. The attenuator is composed of three PIN diodes arranged in a pi configuration. The PIN diodes act as voltage-controlled variable The control voltage is derived from the AGC input to the attenuator shaper stage, which shapes the AGC input for a more suitable RF AGC characteristic. Attenuation is increased by increasing forward bias on the shunt diodes (CR3 and CR5) and reducing forward bias on the series diode (CR6). tenuator shaper will be discussed in a separate paragraph. The attenuator output is applied to IF amplifier stage Q7 which is identical in operation to IF amplifier Q5 described above. The low impedance output from T3 is applied through C40 to second mixer U2.

Second LO Amplifier, Second Mixer. - The 72.110-72.100 MHz second LO input from the synthesizer is applied to the base of Q3. R21 establishes the correct termination impedance for the synthesizer. Q3 is a common-emitter amplifier stage with degenerative feedback introduced in the emitter circuit by R25 for gain stabilization. The output is developed across a resonant tank circuit composed of C53 and L6. C54 couples the output of the stage to a 15 kHz bandwidth 72.105 MHz center frequency filter. R27 provides the correct input termination for the filter. L7 and C56 tune the filter output which is coupled through C55 and FB5 (a ferrite bead) to the base of Q8. Q8 operates in a manner very similar to Q3. R32 provides degenerative feedback for amplifier gain stabilization. The output is developed across a tank circuit comprising C60, C61, C62,

and L24. C58 is a neutralization capacitor. C61 and C62 form a capacitive voltage divider that matches the output impedance of Q8 to the lower input impedance of Q9. Q9 is a common base amplifier stage. Base bias is developed through R35. R38. and CR4 (a temperature stabilizing diode). C65 holds the base at RF ground. Emitter resistor R34 is a parasitic suppressor. The collector output of Q9 is impedance matched to the LO input of the second mixer by means of the pi network comprising C66, C69, and L26. R40 provides a resistive termination for the network input. The second LO signal is mixed with the 82.805  $\rm MHz$ IF in double-balanced mixer U2. The mixer outut is applied to 250 kHz bandwidth 10.7 MHz filter A2FL1. The pi networks at the input and output of the filter match the high impedance filter to the 50 ohm output circuit of the second mixer. The 10.7 MHz second IF signal is then passed to the 10.7/ 455 converter (A3)

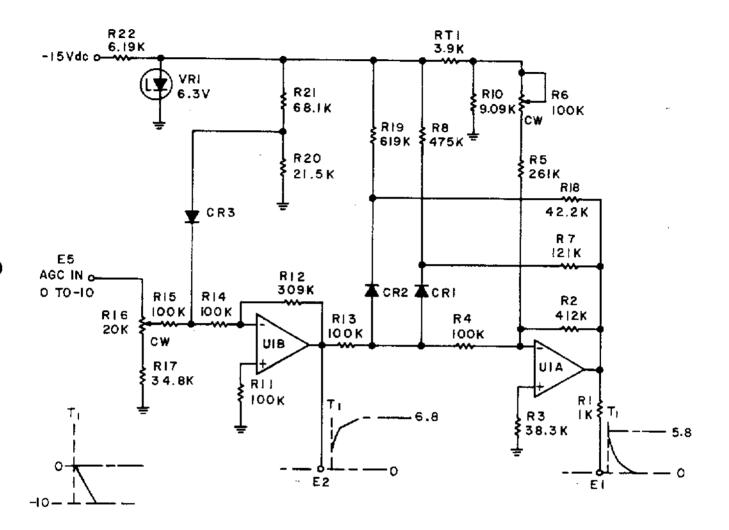

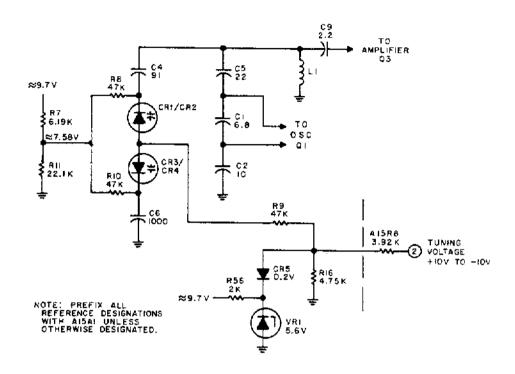

- Figure 7-7 is the schematic diagram of Attenuator Shaper (A2A1). the attenuator shaper. For the purposes of this circuit description, the schematic has been redrawn as shown in Figure 4-3. R22 drops the -15 V dc supply input to -6.3 V dc (stabilized by zener diode VR1). The voltage divider composed of R20 and R21 results in a -1.5 V dc bias on the anode of CR3. AGC voltage, varying from a no-signal level of 0 volts to a strong-signal level of -10 volts is applied at E5 to the input circuitry of amplifier U1B. Since U1B is a linear inverting amplifier, the output voltage should be in linear inverse proportion to the AGC voltage input. This linear relationship exists until the AGC input voltage at E5 causes the voltage at the cathode of CR3 to become more negative than the -1.5 V dc bias on the anode. When this happens, CR3 becomes forward biased causing an increased voltage drop across R15 and R16, thus increasing AGC input voltage attenuation and reducing the net amplifier gain. As a consequence, the output voltage of U1B at E2 rises in linear inverse proportion to the applied AGC input until CR3 becomes forward biased, resulting in a +6.8 V dc 'break point" at U1's output. A further increase in AGC voltage results in greater output from U1B, although the output increases at a lower rate due to the lower amplifier gain caused by CR1 after the "break point" voltage is reached. This shaped voltage is applied to the inverting input of U1A through R13 and R4. Under 0 V dc AGC input conditions, the output of U1A is at its quiescent level of +5.8 V dc due to the negative bias applied to the inverting input through R5. The negative bias is taken from the voltage divider comprising temperature-stabilizing thermistor The +5.8 V dc output of U1A results in cathode biases of +3.35 V dc and +5.0 V dc on CR1 and CR2 respectively, while both anodes are biased at a level just under 0 V dc (the quiescent output level of U1B). As the AGC voltage at E5 becomes negative, the anode voltage of CR1 and CR2 rises. At the same time, the inverted output of U1A causes the cathode voltages of CR1 and CR2 to fall. Eventually, CR1 becomes forward biased, effectively shunting R7 across R2, increasing amplifier negative feedback and reducing gain, (i.e., establishing a "break point" in the amplifier output characteristic). As the AGC voltage at E5 continues to become more negative, CR2 will also become forward biased, establishing another "break point". The E2 output (with a single "break point") is applied to the shunt diodes in the PIN diode attenuator. The E1 output is a composite of the characteristics of U1A and U1B, and exhibits three break

WJ-8888

Figure 4-3. Simplified Schematic Diagram of Attenuator Shaper

points and four slopes. This output is used to control the series diode in the PIN diode attenuator. The shunt diode is controlled by the output of U1B.

4.3.2.4 Type 791198 10.7/455 Converter (A3). - Figure 7-8 is the schematic diagram for the 10.7/455 converter. The 10.7 MHz IF from J2 of the input converter (A2) is amplified, filtered and down-converted to 455 kHz. The 455 kHz third IF is filtered and amplified before being passed to the next receiver stage.

Q1 and Q2 comprise a 10.7 MHz cascode amplifier. The 10.7 MHz second IF is applied to the base of Q1 through C1. R2 and R3 form a base-bias voltage divider for Q1. R1 and C2 form a degenerative feedback path that improves the signal handling capability of the stage. Degenerative feedback in this form, however, lowers the input impedance of the stage. To counteract this, unbypassed emitter resistor R4 is used to introduce degenerative feedback which raises the impedance of the stage. The output of the cascode stage is developed across RF choke L2 and applied to an impedance-matching pi-network comprising C7, C8, and L3. R7 establishes the output impedance of Q2. FL1 is a 250 kHz

bandwidth ceramic filter. C9, C10 and L4 match the output impedance of the filter to the lower input impedance of mixer U1.

The 11.155 MHz LO input from the synthesizer is applied to the base of Q5 through C29, Y1, and C20. Y1 serves as a series resonant filter to suppress spurious inputs from the synthesizer. R29 and R13 establish the termination impedances for the filter, while C29 is used to tune the filter to precisely 11.155 MHz. Q5 is a common-emitter amplifier stage. R18 developes negative feedback. Collector output is developed across L10, which resonates with circuit capacitances to 11.155 MHz. The output of Q5 is applied through R19 and C23 to the base of Q6.Q6 is a common emitter amplifier stage similar to Q5. Collector output is applied to the LO input of balanced mixer U1 through an impedance matching network comprised of C27, C28, and L12, and a 3 dB pad comprising R26, R27, and R28. R23 is a parasitic suppressor.

U1 mixes the 10.7 MHz IF with the 11.155 MHz LO input to produce sum and difference frequencies. A low-pass filter and impedance matching network comprising C12, C13, C14, L5, and L6 attenuates the sum component while permitting the 455 kHz difference component to pass to the input of common gate amplifier Q4. Temperature-stabilized source bias for Q4 is provided by constant current generator Q3 and temperature compensating diode CR1.

4.3.2.5 Type 72399-(X) IF Filter Assembly (A4, A6). - Figure 7-9 is the schematic diagram for the IF filter assembly. The assembly consists of two identical boards (A4 and A6), each mounting up to three 455 kHz mechanical filters. Control voltages from the receiver register are used to switch the selected filter into the signal path. Relays at the input of each filter are used for input switching while FET amplifiers are used for output isolation. Filter control outputs are applied to a subsequent IF amplifier stage, and activate either a narrowband or wideband IF amplifier, depending upon the bandwidth of the selected IF filter. This will be discussed in more detail under the 455 kHz IF amplifier (A8) circuit description.

The 455 kHz IF signal from the 10.7/455 converter (A3) is applied simultaaneously to relays K1, K2, and K3. Detail A on the schematic diagram shows the internal wiring of the normally open, SPST relays. Assuming that IF filter FL1 has been selected, a voltage from the receiver register is applied to the base of Q1 (the bases of Q4 and Q7 remain at ground potential), turning this Most of Q1's collector current flows through the base-emitter transistor on. junction of Q2, causing it to saturate. Since the coil of relay K1 is in the collector circuit of Q2, K1 is activated, permitting the 455 kHz IF signal to be applied to FL1, and to gate #1 of isolation amplifier Q3. The positive voltage drop across the series combination of R5 and the relay coil is applied through R8, R11, and R12 to gate #2 of Q3, turning this amplifier on and permitting the IF signal at gate #1 to be amplified and applied to the next stage through R48 and C24. Since Q6 and Q9 receive 0 volts bias on gate #2 and the sources are all positively biased by R30, very little drain current flows, minimizing interaction with Q3. CR1 protects Q2 from potentially large negative voltages induced by the collapse of the magnetic field of K1 when the relay is de-energized. CR2 is part of an AND gate circuit. R12 is an IF gain adjustment. Operation of the other filter/

amplifiers is the same as described above. R12, R28, and R43 are IF gain adjustments set to equalize the gain of the filter amplifiers.

Type 72409 455 kHz IF Amplifier (A8). - Figure 7-11 is the schematic diagram for the 455 kHz IF amplifier. The first two stages are gain controlled dual-gate MOSFET amplifiers. The output of Q2 is applied simultaneously to a narrowband IF amplifier comprising Q3 and Q5, and a wideband IF amplifier comprising Q4 and Q6. The amplifier used is determined by the filter control outputs from A8. These switched outputs are wired to provide base bias for either the wideband or narrowband amplifiers, activating one and The wideband amplifier is activated when the filters greater disabling the other. than 2 kHz bandwidth are used, while the narrowband amplifier is activated when the 2 kHz or narrower bandwidth filters are used.

Q1 and Q2 are cascaded gain-controlled MOSFET amplifiers. The 455 kHz signal from the IF filter assembly is applied through C1 to gate #1 of amplifier Q1. The drain output of Q1 is developed across L1 and applied through C6 to gate #1 of Q2. The drain output of Q2 is developed across L2. IF output is taken from the arm of gain control potentiometer R16. Gate #1 bias for Q1 and Q2 is developed by voltage dividers R1-R2 and R9-R10 respectively. Gate #2 of Q1 is biased at approximately +3.5 V dc by R3, R5, and CR1 at 0 V AGC input. The bias on gate #2 of Q1 does not fall until the AGC voltage becomes sufficiently negative to reverse bias CR1, effectively removing it from the circuit. Further negative increases in AGC voltage will then be reflected in a more negative bias on gate #2 of Q1, reducing the amplifier gain. Identical AGC circuitry is used for Q2.

The IF signal output from Q2 is applied simultaneously to narrowband and wideband IF amplifiers comprising Q3-Q5 and Q4-Q6, respectively. As mentioned above, switched +15 V dc supply lines determine which of the two amplifiers will be activated (activation is achieved by applying the switched +15 V dc source to the base bias voltage divider of the desired amplifier). Assuming that the wideband amplifier (Q4-Q6) is activated, the IF signal is amplified by common emitter R32 provides degenerative feedback for improved signal handling capability, while R34 and R28 act as parasitic suppressors. Tank circuit C22-L5 develops the collector output. C25 couples the signal to an impedance matching network composed of L6, C26, and C27, which steps down the circuit impedance. Loading resistor R36 broadens the frequency response of the interstage coupling Output is provided by emitter follower amplifier Q6. Operation of the narrowband amplifier (Q3-Q5) is very similar to that of the wideband amplifier, although some component values differ, and no loading resistor is used. Interaction between the amplifier outputs is minimized due to the isolation provided by the reverse bias on the base-emitter junction of the inactive emitter follower.

4.3.2.7 Type 791113 AM Demodulator (A9). - Figure 7-12 is the schematic diagram of the AM demodulator. The 455 kHz IF signal is amplified and applied to a diode detector. The resultant audio signal is then amplified. A noise limiter in the audio section reduces the intensity of impulse-type noise.

The 455 kHz signal from the 455 kHz IF amplifier (A8) is applied to gate #1 of Q1 through C1. Q1 is a common source amplifier, with its drain output developed across L1. R9 loads L1 to reduce resonant effects. Bias for gate #1 of Q1 is obtained from voltage divider R1-R2. Gate #2 is used for gain control. The output of Q1 is applied to the base of isolation amplifier Q2.

Q2 develops both emitter and collector outputs, each 180° out of phase with the other. The emitter output drives Q4, another isolation amplifier. The emitter output of Q4 is coupled through C16 to board pin 5 (IF OUTPUT), and then routed to the LSB, USB/CW, and FM demodulators. The collector output is transformer coupled, and made available as an IF output at board pin 1. From board pin 1, the IF signal is routed to the IF OUTPUT jack (J8) on the main chassis.

The collector output of Q2 is applied through C7 to the base of common emitter amplifier Q3. Base bias is developed by R15-R16. R22 introduces degenerative feedback. The collector output is developed across the primary of T1 and its resonating capacitor, C24. R21 is a parasitic suppressor. R36 loads the resonant output circuit to optimise the frequency response.

The AM detector is a full-wave center-tapped rectifier circuit. Diodes CR3 and CR4 are used as detectors (rectifiers). A slightly positive bias is applied to the anodes of the diodes to overcome the diode barrier potentials to increase linearity and measure the sensitivity of the detector. The rectified output is developed across R27. C14 filters out the 455 kHz component of the rectified output. This rectified and filtered signal is then applied to emitter follower Q5.

The AM detector output from Q5 is applied to a noise limiter circuit comprising CR5, CR6, Q6, Q7, Q8, and associated resistors and capacitors. When activated, the noise limiter limits man-made and atmospheric impulse-type noise to just under twice the average AM detector output level (approximately 90% of the peak AM detector output level).

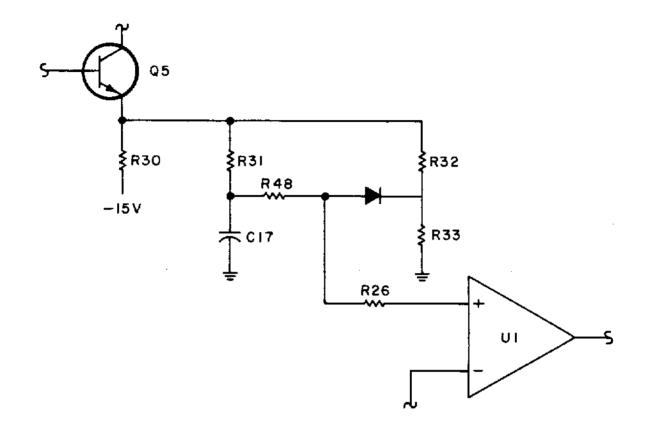

For clarity, a simplified noise limiter circuit diagram is presented. Referring to Figure 4-4, assume that the noise limiter has been activated (this will be explained in the following paragraph). The (positive) AM detector output of Q5 is applied to time constant circuit R31-C17. The long time constant results in C17 being charged to the average AM detector output voltage. The AM detector output of Q5 is simultaneously applied to voltage divider R32-R33. R32 and R33 is such that for a 90% modulated AM signal, the resultant peak voltage at the cathode of CR5 is approximately equal to the average voltage at the Consequently, CR5 will be forward biased as long as the AM deanode of CR5. tector voltage at the cathode of CR5 is not greater than the 90% modulation level. Disregarding for the moment the 0.6 V diode barrior potential that must be overcomve, the forward biased diode will permit the detected AM voltage to be passed through CR5 and R26 to audio amplifier U1. If a sudden noise pulse occurs, the signal voltage at the cathode of CR5 rises accordingly. The long time constant of R31 and C17, however, prevents the average voltage through R48 at the anode of CR5 from also rising. Since the diode becomes momentarily reverse biased, no output is applied through R26 to audio amplifier U1. Thus, sudden noise burst are limited in amplitude to 90% of the peak demodulated signal voltage, resulting in effective noise limiting.

WJ-8888

Figure 4-4. Noise Limiter, Simplified Diagram

The simplified circuit is modified somewhat to provide a means of eliminating the effect of the barrier potential of CR5 and switching the noise limiter on or off as desired. Referring back to Figure 7-12, the positive AM demodulator output of Q5 is applied to averaging circuit R31-C17, just as in the simplified The averaged output voltage from C17, however, is applied through R48 to the anode of CR5 via emitter follower Q7. Q5's output voltage is also applied to the cathode of CR5 via R32 and R33, with C22 providing high frequency rolloff. In the simplified circuit diagram the voltage dividing action of R32 and R33 reduced the signal voltage at the cathode of CR5 to the point where an AM detector output signal of 90% modulation or less resulted in a lower voltage on the cathode of CR5 than on the anode. In order for the diode to conduct, however, a forward bias of 0.6 volts is required to overcome the diode barrier potential. Thus in the simplified circuit diagram, the barrier potential would require a lower voltage at the cathode of CR5 for conducting to begin. This directly implies then that the signal level at which CR5 would reverse bias would be lower, thus resulting in limiting occurring at signal modulation levels well under 90%. This would be undesirable since the clipped signal would be distorted. In the actual circuit, the diode barrier potential is counteracted by the 0.6 volt base-emitter drop of Q7, which raises the anode voltage of CR5 by 0.6 volt, thus negating the effect of the barrier potential of CR5.

The noise limiter is activated by a positive input (from the receiver register) to board pin 4 (AM NL) that turns Q6 on and Q8 off. Under these circumstances, the noise limiter operates as described above. To disable the noise limiter, a ground potential (from the receiver register) is applied to board pin 4 (AM NL) that turns Q6 off and Q8 on. This results in a positive voltage applied to the base of Q7 through Q8, CR6, and R49. The increased positive voltage at the base of emitter follower Q7 causes the emitter voltage of that transistor to rise by a like amount, resulting in a positive bias applied to the anode of CR5 through R48. The magnitude of this positive bias is sufficient to forward bias CR5 under all signal conditions, effectively disabling the noise limiter.

U1 is an audio amplifier with a high impedance input and a low impedance output. The AM DET OUTPUT (board pin 8) is applied to the gain control board (A14) while the AM DET MONITOR (board pin 12) output is routed to the AM MONITOR jack (J7) on the receiver main chassis. R39-C20 and R40-C21 are low-pass filters used to provide high frequency roll-off.

4.3.2.8 Type 791162 FM Demodulator (A10). - Figure 7-13 is the schematic diagram of the FM demodulator. The input comes from the IF output amplifier on the AM demodulator board (A9). The 455 kHz IF signal is limited in amplitude by a high gain limiting amplifier and demodulated in an FM detector. The resultant audio is then amplified.

The 455 kHz IF signal from the AM demodulator is applied through C1, R1 and C2 to the input of U1. U1 functions as a high gain symmetrical current mode limiter. The limiting action results in a constant output amplitude over a wide range of input signal amplitudes, thus ensuring that all AM signal components are eliminated.

After limiting, the signal is passed to the Foster-Seely FM discriminator. Discriminator transformer T1 has both its primary and secondary circuits resonated at 10.7 MHz. C10 introduces a quadrature component of the primary voltage to the secondary center tap. This causes the primary voltage of T1 to be 90° out of phase with the entire secondary voltage at the 455 kHz center frequency. The vectoral addition of these voltages results in equal amplitude ac voltages at the anodes of CR1 and CR2. The resultant rectified dc voltages are of equal amplitude and opposite polarity, and therefore cancel, resulting in no output to U2. If the signal frequency deviates from the 455 kHz center frequency, the 90° phase relationship changes, with the result that the voltage amplitude at the anode of one of the diodes will exceed that of the other. As a consequence, the rectified dc voltages will reflect the amplitude difference, and a net output to U2 will result. Since the instantaneous output voltage is proportional to the frequency difference between the instantaneous signal frequency and the 455 kHz center frequency, the resultant output in effect is a reproduction of the modulation of the FM carrier. C13 helps to filter out 455 kHz signal components.

The demodulated signal is passed to voltage follower U2. The two available audio outputs are the FM DETECTOR MONITOR output (routed to J9 on the main chassis) and the FM AUDIO output, which is applied to the audio amplifier (A13).

Q1, Q2, Q3, and Q4 comprise a switched 455 kHz IF amplifier that is active only during either CW mode. It's purpose is to provide an IF signal to the USB/CW demodulator that bypasses the 2.7 kHz bandwidth USB filter (see Figure 7-14), since this filter would otherwise cause gain variations across the IF passband in CW operation. A positive output level (generated in the CW modes only) at board pin 7 (CW(s)) activates a diode switch in the USB/CW demodulator that shunts the USB filter, eliminating any 455 kHz feedthrough from that source.

Referring back to Figure 7-13, the 455 kHz IF input to the FM demodulator is also applied through R17 and C16 to the base of Q3, a common emitter amplifier with degenerative feedback introduced into the emitter circuit by R23. The collector output of Q3 is dc coupled to the base of emitter follower Q4. The output of Q4 is applied through C20 and R26 to the CW input of the CW/USB demodulator. Q3 and Q4, however, can only amplify the 455 kHz signal if the receiver is in either CW mode of operation. Assuming that a CW mode has been selected by the operator, either the CW V (CW mode using the variable frequency BFO) or the CW F (CW mode using the fixed frequency BFO) inputs at board pins 15 and 16 respectively will be positive. The positive input causes collector current to flow through Q1, which also turns on Q2. As long as Q2 remains on, Q3 and Q4 will receive the positive voltage required for operation, and will function as described above. The switched voltage is also applied through CR6 to board pin 7, and routed to the CW/USB board. If the CW V and CW F inputs are disabled (grounded), however, Q1 and Q2 will no longer conduct, resulting in amplifiers Q3 and Q4 being disabled and no positive output at board pin 7. The CW V and CW F inputs are controlled from the receiver register.

4.3.2.9 Type 791180-(X) LSB/USB/CW Demodulator (A11, A12). - Figure 7-14 is the schematic diagram of the LSB and USB/CW demodulators. Other than the difference in component values shown on the schematic, both demodulators are identical. For either LSB or USB reception, the 455 kHz IF signal from the AM demodulator (A9) is amplified and applied to 2.7 kHz bandwidth filter (the center frequency of the LSB filter differs slightly from that of the USB filter) and then to a double-balanced modulator/demodulator where the signal is mixed with the BFO input. The audio (difference) frequency output of the double-balanced modulator/demodulator is then amplified and made available as two audio outputs. The audio signal is also applied to an AGC detector and amplifier, and the resulting AGC voltage is used to control the gain of the input 455 kHz amplifier stage if the ISB detection mode has been selected. The USB demodulator is also used for demodulation of CW signals, as will be explained in detail in a subsequent paragraph.

The 455 kHz IF signal from the AM demodulator (A8) is applied to voltage divider R1-R2. The attenuated signal is then applied through C1 to gate #1 of Q1. Voltage divider R3-R4 provides the proper dc bias for gate #1. The amplified signal is developed across L1 and R5, and coupled through C5 to the base of Q2. L1 resonates with internal and circuit capacitances to 455 kHz, while R5 loads L1 to broaden the bandpass. Q2 is a common emitter amplifier stage with degenerative feedback introduced into the emitter circuit by R13 and R14. R14 controls the stage gain by varying the amount of degenerative feed-

back. Collector output is developed across R11 and applied to bandpass filter FL1 through C9. Voltage divider R8-R9 provides base bias for Q2.

The bandpass of FL1 on the LSB board (A12) extends approximately from 452.0-454.7 kHz, while the bandpass of FL1 on the USB/CW board (A11), extends approximately from 455.3-458.0 kHz. C10 and C12 are filter termination capacitors. The filter output is coupled through C27, C28, R22, and C15 to the input of double-balanced modulator/demodulator U1. For LSB or USB reception, CR5 is reverse biased by the negative voltage at its anode produced by current flowing through R65 and R66 to the (grounded) CW(S) terminal (board pin 19). The CW(S) input comes from the FM demodulator board, and is held near ground potential in the LSB and USB modes of operation. As a result, CR5 has no effect on circuit operation for these modes of reception. For CW reception, however, a positive voltage at the CW(S) input (from the FM demodulator board) forward biases CR5, causing the output of FL1 to be shunted to ground, preventing any FL1 output from reaching U1. Instead, the 455 kHz IF signal from the switched IF amplifier on the FM demodulator board (A10) applied to the CW IF INPUT (board pin 5) is applied through C25 and C15 to the signal input of U1.

U1 receives the IF signal at pin 1 and mixes it with the BFO signal applied to pin 7. The BFO signal (from the BFO synthesizer) is first amplified by common emitter stage Q3. R17 and R18 form a base bias voltage divider, R21 develops degenerative feedback for the stage, and R20 is the collector load resistor. The collector output is applied through C14 to pin 7 of U1. The output of U1 at pin 9 contains sum and difference frequencies, but C19 prevents the sum frequency from being passed. Only the audio difference frequency is coupled through C20 and R33 to the input of audio amplifier U2. VR1 drops the -15 V dc supply to approximately 8.2 volts, and applies this voltage to pin 10 of U1. R24-R25 and R26-R27 are voltage dividers that are used to provide proper biasing voltages for U1. R28 establishes the conversion gain, and R30 and R31 are the load resistors for the differential output. Since only a single-ended output is required, C17 is used to RF bypass pin 6 of U1. R31 is a voltage dropping resistor, R29 establishes the internal bias of U1, and L2 is an RF choke that holds the BFO input of U1 (pin 7) at dc ground potential.

Audio amplifier U2 uses a frequency sensitive degenerative feedback circuit to produce high frequency audio roll-off. R35, the amplifier negative feedback resistor, is shunted by C21. At low audio frequencies, the reactance of C21 is high compared to the resistance of R35, and can be disregarded. At higher audio frequencies, however, the reactance of C21 becomes sufficiently low to significantly increase the inverse feedback (and reduce the gain) of U2. Thus, high audio frequencies receive less gain. The audio signal is then passed through R37 to the SSB/CW AUDIO output terminal (board pin 6). The audio signal is also applied through R38 to T1. The SSB/ISB OUTPUT from the secondary of T1 is made available as an audio output at J10 of the main chassis (AUDIO OUTPUT).

An AGC circuit is comprised of Q4-8, CR1-4, U3 and associated components. The audio output of U2 is detected, processed, and applied to gate 2 of Q1 to provide independent AGC action for the demodulator in the ISB mode of operation.

The output of U2 is applied to the base of Q8. The low impedance emitter output rapidly charges C24 to the peak audio signal level. Since CR6 prevents C24 from discharging into the emitter of Q8 when it becomes less positive than the voltage across C24, the discharge time constant is determined primarily by C24 and R59 (the high impedance input of JFET Q7 can be disregarded). Thus, the AGC detector circuit exhibits the desired fast attack, slow decay characteristic.

High impedance source follower Q7 is employed to provide isolation for the AGC time constant circuit (R59 and C24). The output of Q7 is applied through R56 to the input of emitter-driven amplifier Q6. R39 adjusts the threshold level of the AGC voltage. The collector output of Q6 is developed across R53. This voltage is then applied through R52 to the inverting input of amplifier U3. R51 and R63 cause the output of U3 to be positive under zero-signal input conditions (to properly bias gate #2 of gain-controlled amplifier Q1for ISB operation).

In the ISB mode of operation independent AGC is provided for each side-band demodulator. A switch (activated by the receiver register) raises the gain of Q1 as required to maintain constant output. Thus, the separate ISB AGC loops in the sideband demodulators permit independent AGC action for each received sideband. The remainder of this sub-section discusses the ISB AGC circuitry in greater detail.

If the receiver is operated in any mode other than ISB, the ISB control input (board pin 7) from the receiver register is held near ground potential, shutting off Q4 and Q5. Under these circumstances, current from the -15 V dc supply through R62 flows through CR1, causing a reduction of the positive bias on gate #2 of Q1, reducing Q1's gain and preventing ISB AGC action. ISB mode of operation, however, the ISB control input receives a positive voltage from the receiver register turning on Q4 and Q5. This results in a relatively high positive voltage at the collector of Q5 that is applied to the cathode of CR1. Since this voltage exceeds the voltage at the anode, CR1 becomes reverse biased permitting the voltage applied to gate #2 of Q1 to rise to its normal (positive) value as determined by the output of U3. The positive voltage at the cathode of CR2 exceeds the +1.2 volts at the anode (caused by the voltage drop across CR3 and CR4), and CR2 also becomes reverse biased. Thus, the positive gain control voltage applied to gate #2 of Q1 can drop to as low as +0.6 volts (the bias voltage at the anode of CR2 less CR2's 0.6 volt barrier potential) before CR2 becomes forward biased and clamps the voltage at that level. Diode CR2 becomes forward biased when the gain control voltage exceeds approximately +7.0 volts, clamping the voltage at that level.

4.3.2.10 Type 7453 Audio Amplifier (A13). - Figure 7-15 is the schematic diagram of the audio amplifier. The three audio inputs (from the demodulators or gain control board) are applied to a transistor switching network. The selected audio signal is then applied to a squelch gate, after which it is amplified. The amplified signal is made available as the audio line output. Part of the signal is sampled, rectified, and used to drive the audio output meter. Also included on this board is a separate amplifier that is used to build up the level of the audio signal applied to the headphone output circuitry.

The audio inputs to the audio amplifier board come in at board pins 6 (FM), 8 (FM and ISB), and 12 (ISB). The FM input comes directly from the FM demodulator (A10). The FM and ISB input comes from the gain control board (A14), where an electronic switch selects either the output of the AM demodulator (A9), or the LSB or USB/CW output from the LSB/USB/CW demodulators (A11, A12) when the LSB, USB, or CCW (but not ISB) mode of operation has been selected.

The audio inputs are applied to an electronic switching network composed of Q1-Q6. The FM audio input is applied through R10 and C1 to the collector of Q5. From this point, it is passed through C4 and R16 to the source of squelch gate Q7. The FM and ISB audio input is applied through R12 and C2 to the collector of Q4. From this point, it is passed through C5 and R17 to the source of squelch gate Q7. Similarly the ISB audio input is applied through R14 and C3 to the collector of Q6. From this point it is passed through C6 and R18 to the source of squelch gate Q7. It is assumed in each case above that Q5, Q4, and Q6 are in the off states. In actual operation, the transistor associated with the selected audio input is off, permitting the signal to be applied to the squelch gate while the other transistors are turned on to short their respective signals to ground. As a result, only the selected signal is passed to the squelch gate.

If the FM detection mode has been selected, a positive potential from the receiver register at board pin 5 (FM) turns Q1 on and Q5 off. With Q5 off, the FM audio input at board pin 6 is free to pass through R10, C1, C4, and R16 to The near-ground potential at the collector of Q1 places a forthe source of Q7. ward bias on CR1, which lowers the base bias on Q3 (CR1 effectively shunts R8 and R9 when forward biased). As a result, Q3 turns off, permitting a higher potential to be felt at the base of Q4, turning that transistor on. . With Q4 on, the FM and ISB audio input at board pin 8 is shunted to ground through R12 and C2. At the same time, board pin 9 (ISB) receives a near-ground potential from the receiver register, holding Q2 in the off state, with the result that Q6 is turned on, shunting the ISB audio input at board pin 8 to ground through R14 With Q5 off, Q4 on, and Q6 on, the desired FM audio input passes to the source of Q7, while the remaining audio inputs are shunted to ground.

If the ISB detection mode has been selected, a positive potential from the receiver register at board pin 9 (ISB) turns Q2 on and Q6 off. With Q6 off, the ISB audio input at board pin 12 is free to pass through R14, C3, C6, and R18 to the source of Q7. The near-ground potential at the collector of Q2 places a forward bias on CR2, which lowers the base bias on Q3 (CR2 effectively shunts R8 and R9 when forward biased). As a result, Q3 turns off, permitting a higher potential to be felt at the base of Q4, turning that transistor on. With Q4 on, the FM and ISB audio input at board pin 8 is shunted to ground through R12 and C2. At the same time, board pin 5 (FM) receives a near-ground potential from the receiver register, holding Q1 in the off state, with the result that Q5 is turned on, shunting the FM audio input at board pin 6 to ground through R10 and C1. With Q5 on, Q4 on, and Q6 off, only the desired ISB audio input passes to the source of Q7, while the remaining audio inputs are shunted to ground.

If the AM, LSB, USB, or CW detection modes are selected, near-ground potentials from the receiver register are applied to board pins 5 and 9, turning

Q1 and Q2 off. The resulting high potentials at the collector of these transistors cause both CR1 and CR2 to become reverse biased. In turn, full base bias is then permitted to be felt at the base of Q3, turning that transistor on. The resulting low potential at the collector of Q3 turns Q4 off, with the result that the FM and ISB audio input at board pin 8 is free to pass through R12, C2, C5, and R17 to the source of Q7. At the same time, the high potentials at the collectors of Q1 and Q2 cause both Q5 and Q6 to be turned on, resulting in both the FM and ISB audio inputs at board pins 6 and 12, respectively, being shunted to ground. With Q5 on, Q4 off, and Q6 on, only the desired FM and ISB audio input passes to the source of Q7, while the remaining audio inputs are shunted to ground.

FET Q7 is the squelch gate that receives the selected audio signal from the audio switching network. With no voltage applied to the gate of Q7 the FET conducts, permitting the selected audio signal to be applied to audio amplifier U2. A negative voltage at the gate of Q7 cuts that transistor off, preventing any audio signals from reaching U2.

Ut is an operational amplifier that is used to control squelch gate Q7. Positive feedback through resistors R21 and R22 set the gain of U1 with a controlled hysteresis. As a result, U1 behaves more as a hysterisis switch than as an amplifier, since a positive voltage at pin 2 (the non-inverting input) causes the output voltage at pin 6 to swing to nearly -15 volts (cutting off Q7), while a negative voltage at pin 2 causes the voltage output at pin 6 to swing to nearly +15 volts. Since CR3 becomes reverse biased, the +15 volt output is not felt at the gate of Q7. The removal of the negative bias from the gate of Q7, however, is sufficient to allow Q7 to conduct. The hystersis caused by the positive feedback applied to U1 prevents the switching threshold from being too narrow.

The input to U2 (pin 2) comes from a voltage divider composed of R19 R19 receives voltage from squelch control potentiometer on the main chassis (Figure 7-33). The squelch control voltage can be set to any value R20 receives gain control voltage from the gain control between 0 and +5 volts. The AGC voltage is negative, and proportional to the average amboard (A14). plitude of the received signal. If the AGC voltage is small, the positive squelch control voltage causes the resultant voltage at the junction of voltage divider resistors R19 and R20 to be positive. As explained previously, a positive voltage applied to inverting input pin 2 of U1 causes the output voltage at pin 6 to become negative, shutting off the squelch gate (Q7) and preventing any audio from reaching the input of the audio amplifier. If the receiver is then tuned to a signal strong enough to produce sufficient negative AGC voltage to overcome the positive squelch control voltage at pin 2 of U1, causing that input to become negative, the output at pin 6 swings positive, causing the squelch gate to conduct and permitting the audio signal to pass through to audio amplifier U2. Thus, the receiver produces an audio output only for signals in excess of a certain average amplitude. This level, or threshold, is determined by the setting of R6 on the main chassis.

U2 amplifies the audio signal from squelch gate Q7. The output of U2 at pin 6 is coupled through R30 to the primary of T1. The secondary audio voltage is applied to board pins 21 and 22, and is then routed to the line audio terminals of J10 on the main chassis. The voltage at the output of U2 is also applied to a voltage doubler rectifier circuit comprising C11, R33, CR4, CR5,

R34, and C12. The rectified audio voltage is then applied to the front panel meter (M1 on yhe main chassis) through R35 and R36, as long as a near-ground potential from the receiver register is applied to the MTR input of the board (pin 18) permitting the base of Q9 to receive negative bias. The ground potential causer Q9 to conduct, causing Q8 to turn off. As long as Q8 remains off, the rectified audio voltage can be applied to the front panel meter. The meter can also be used, however, as a signal strength meter. In this case, the negative voltage at the MTR input of the board becomes positive, turning Q9 off and permitting Q8 to conduct. This in turn shorts the output of the rectifier circuit to ground and prevents any output from being applied to the front panel meter. The operation of the front panel meter as a signal strength indicator will be discussed in a subsequent paragraph.

The audio output from pin 6 of U2 is also coupled through R44 to board pin 20 (AUDIO). From pin 20, the audio signal is routed to a 10,000 ohm audio gain control potentiometer (R7) on the main chassis (Figure 7-33). The arm of the potentiometer is routed back to the PHONE AMPL INPUT (board pin 1) of the audio amplifier board. The signal is then applied through R27 to pin 2 of U3. U3 amplifies the signal, and couples its output at pin 6 through R32, C10, and C13 to board pin 19 (PHONES OUTPUT). From this point, the signal is routed to the headphone jack assembly (A28). Electrolytic capacitors C10 and C13 are connected "back-to-back" to provide high-capacitance ac blocking (a single electrolytic capacitor would not be suitable for handling the ac output of U3). Note that the audio gain control potentiometer (R7 on the main chassis) controls only the amplitude of the headphone output and has no effect on the amplitude of the audio line output signal.

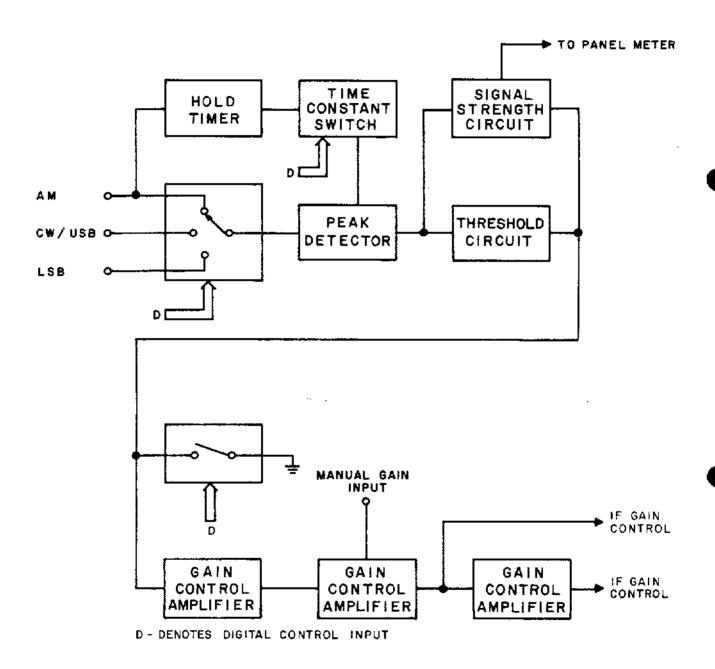

4.3.2.11 Type 7899 Gain Control (A14). - Figure 7-16 is the schematic diagram of the gain control. The purpose of this circuit is to derive gain control voltage from the appropriate audio input, process this voltage to achieve the desired gain control characteristic, and apply the voltage to the gain controlled stages in the RF and IF sections of the receiver. Three gain control modes are available to the receiver operator: NORM AGC (normal automatic gain control), HOLD AGC (hold automatic gain control), and MAN (manual gain control). NORM AGC gain mode is selected, an AGC voltage with a fast-attack fast-decay characteristic is produced. This type of AGC characteristic is suitable for AM. FM, and CW reception. In addition, this gain mode is automatically selected whenever the receiver is operated in the ISB detection mode. The HOLD AGC gain mode is most suitable for LSB/USB reception, where a fast-attack delayeddecay characteristic is desired (a two second delay is provided, although the delay time may be changed). In the MAN gain mode, no signal-derived gain control voltage is produced. Instead, the gain control voltage (and hence the receiver gain) is set manually by the front panel RF GAIN control (the RF gain control also functions in the AGC gain modes).

A functional block diagram of the gain control is shown in Figure 4-5. Audio inputs from the AM, USB/CW, and LSB demodulators are applied to an electronic switch which selects the audio signal appropriate for the detection mode (for the FM detection mode, the AM demodulator input is utilized for AGC

purposes). Assuming that the NORM AGC gain mode has been chosen by the operator, the selected audio input is applied to a peak circuit which produces a voltage proportional to the peak signal input level. This voltage is then applied to a threshold circuit that permits automatic gain control action only for signals above a certain predetermined threshold (the AGC is thus "delayed", and does not act for weak signals below the threshold level). Both the input and output of the threshold stage are applied to the signal strength circuit which buffers the AGC voltage and drives the signal strength meter on the front panel if this mode of metering has been selected (the meter can also be used to indicate the line audio output power as previously described). The threshold stage also drives a gain control amplifier which provides gain control voltage to the appropriate receiver IF stages. The output of the gain control amplifier is applied to a second gain control amplifier as well. The output of this stage is then applied to the attenuator shaper (A2A1) for RF gain control.

In the HOLD AGC gain mode, operation of the gain control circuits is the same as described above. In addition, however, the digital control input to the time constant switch causes the time constant of the peak detector to increase. The peak of the audio input from the AM demodulator is stored by the hold timer circuit (regardless of the detection mode). When the signal level drops, the timing circuit is activated, and after the delay interval (normally two seconds) reverts the peak detector time constant back to its normal fast-decay characteristic via the time constant switch.

In the MAN gain mode, the digital control inputs cause the output of the threshold circuit to be shunted to ground. The receiver gain is then controlled exclusively by the manual gain circuitry.

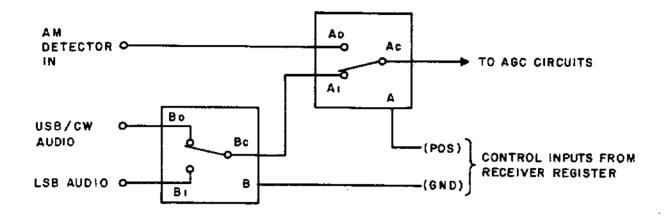

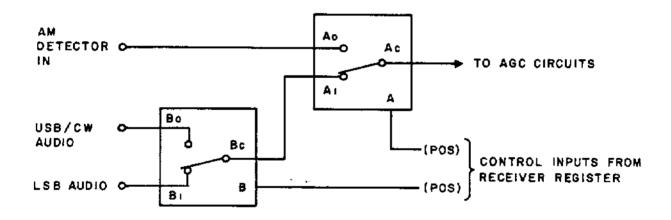

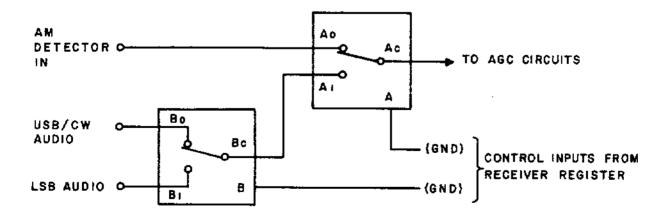

Referring to Figure 7-16, the gain control inputs are the audio outputs from the AM demodulator, the USB/CW demodulator, and the LSB demodulator. The audio signals are applied to the inputs of digitally controlled electronic switches U1A and U1B, which select the appropriate audio input. The switches are activated by digital control inputs from the receiver register. U1B, for example, has the USB/CW and LSB audio inputs applied to Bo (pin 2) and B, (pin 1), respectively. As long as the B control input (pin 10) is at ground potential, only the  $B_0$  input will be internally coupled to the output at Bc (pin 15). If a positive voltage (from the receiver register) is applied to the LSB control input (board pin 16), that potential will be felt at the B control input of U1B, causing the device to prevent the  $B_0$  input (USB/CW audio) from reaching the output at  $B_0$ . Instead, the B, input (LSB audio) is now internally coupled to Bc. U1B then, can be viewed essentially as an electronically controlled SPDT switch. With no voltage applied to  $B_{\boldsymbol{c}}$  is made to  $B_{\boldsymbol{c}}$  , and when a positive voltage is applied to B, B, is made to  $B_{\text{C}}$ . The LSB/USB/CW output of U1B at  $B_{\text{C}}$  is applied to the A, input (pin 13) of U1A. The Ao (pin 12) input receives the AM demodulator audio signal from board pin 19 (AM DETECTOR IN) through R5. U1A is identical to U1B. A positive control input at A (pin 11) from the receiver register causes A<sub>1</sub> to be internally coupled to A<sub>C</sub> (pin 14), while a ground (or near ground) input at A results in Ao being internally coupled to Ac.

Figure 4-5. Functional Block Diagram, Gain Control (A14)

In the CW FIXED, CW VAR, USB, or ISB/USB detection modes, a positive potential is applied only to the A control input of U1A. As a consequence, U1A selects only the  $A_1$  input from  $B_{\,\text{C}}$  of U1B to be coupled to  $A_{\,\text{C}}$  . positive voltage is applied to the B input of U1B, the USB/CW audio signal is coupled from Bo to Bc , then from Bc to A; (via a hard-wire connection) and from  $A_1$  to  $A_{\,\text{C}}$ . Thus, only the desired USB/CW audio signal appears at the output of the electronic switch for application to the AGC circuitry. In the LSB or ISB/LSB detection modes, the receiver register causes both the A and B control inputs to become positive. As a consequence, the LSB audio signal (at board pin U) is coupled from  $B_1$  to  $B_c$ , from  $B_c$  to  $A_1$ , and from  $A_1$  to  $A_c$ . Thus, only the desired LSB audio input appears at the output of the electronic switch. In the AM detection mode, neither the A nor B control inputs are positive, with the result that only the desired AM audio signal appearing at  $A_{\mbox{\scriptsize 0}}$  is coupled to  $A_{\mbox{\scriptsize C}}$  . In the FM mode of operation, the AM audio input is used for AGC purposes. As a result, operation of the gain control circuitry is identical for both the FM and AM detection modes. Figure 4-6 is a simplified illustration of the signal selection arrangement, substituting SPDT toggle switches for U1A and U1B.

The selected audio output at Ac is applied through R10 to the  $\overline{FM/ISB}$  audio output (board pin 10) from where it is routed to the  $\overline{FM}$  and  $\overline{ISB}$  audio input of the audio amplifier (A13). Q2 is a transistor switch that is activated during the LSB, USB, or CW modes of operation. This switch causes R11 to shunt the  $\overline{FM/ISB}$  audio output terminal, reducing the signal level applied to the audio amplifier (A13) for signal level equalization.

The audio output of U1A (pin 14), is applied to the base of amplifier Q4. The emitter output is dc coupled to the base of emitter follower Q5. itive) audio emitter output of Q5 charges C3 through R18. The voltage applied to pin 5 of U2A is proportional to the peak audio input to R18 and C3. shunts series circuit R18 and C3 (through time constant switch U1C), assuming that the NORM AGC gain mode has been selected (the operation of the time constant switch in the various gain control modes will be discussed in a subsequent paragraph), resulting in a fast-attack fast-decay AGC characteristic. The positive AGC voltage is amplified and buffered by U2A, and applied through R71 and R75 to the non-inverting input (pin 3) of U2B. The output of U2B is applied to CR9. Since that diode passes only positive voltages to the subsequent circuitry, it is necessary that the voltage on the non-inverting input be more positive than the fixed voltage at the inverting input (pin 2). Otherwise, the output of U2B will be negative, reverse biasing CR9, and preventing AGC voltage from being passed to the next stage. The voltage applied to the inverting input is determined by R27, R30, and R34. As a result AGC action can only occur when the AGC voltage at the non-inverting input exceeds the positive threshold voltage at the inverting Thus, delayed AGC action is obtained, and receiver gain is not reduced for weak signals below a predetermined level (2 microvolts) as set by the threshold voltage applied to the inverting input of U2B. This threshold voltage can be reduced by shunting the threshold adjust terminal (board pin 11) to ground through an appropriate value of resistance.

The positive AGC voltage from CR9 is passed through R39 and R42 to the inverting input (pin 2) of U3B. Q9 is turned off in either AGC gain mode,

and therefore has no effect on AGC operation. The AGC output voltage of U3B at pin 1 is negative. CR10 forward biases if a positive voltage appears at pin 1 of U3B causing feedback resistor R47 to be shunted by a low resistance, decreasing the gain of U3B to a very low level. Thus, the output of U3B cannot go positive. R76 provides a small amount of bias for CR10 and the inverting input of U2.

The negative AGC voltage from U3B is applied through R73 to the base of emitter follower Q12. The negative emitter AGC voltage output is applied through R55 to the IF AGC output terminal (board pin 7), and is then applied to the gain-controlled stages in the 455 kHz IF amplifier (A8) and AM demodulator (A9), causing reduced gain in these stages.

In addition to being applied to the base of Q12, the negative AGC voltage from U4B is also applied through R51 to the emitter of voltage level shifter Q13. The voltage output level of Q13 can be adjusted by varying R74. This in turn sets the quiescent AGC output voltage of amplifier U4A. The amplified AGC output at pin 7 of U4A is applied through R62 to the RF AGC output terminal (board pin 4), and from there routed to the attenuator shaper (A2A1) for application to the PIN diode attenuator on the input converter (A2).

In the MAN gain mode, a positive voltage at board pin 12 (MAN) turns on Q6. As a result, Q7 and Q10 turn off. The positive potential at the collector of Q7 turns on Q9. Q9 shunts the positive AGC output voltage from pin 1 of U2B through CR9 and R39 to ground, preventing any further AGC action. The manual gain control voltage at board pin 8 (MANUAL GAIN INPUT) passes through R48, R46, and R43 to the inverting input (pin 2) of U4B. The operation of the subsequent gain control stages remains unchanged. However, they are no longer controlled by AGC voltage (from U2B), but instead by the output voltage from the RF GAIN potentiometer on the main chassis (Figure 7-33). A greater positive manual gain input voltage (caused by rotating the RF GAIN potentiometer counterclockwise) results in more gain reduction.

The RF GAIN control can also be used to reduce receiver gain in the AGC In either AGC mode, Q10 is turned on (by the receiver modes of operation. register via Q6 as described above) resulting in the bottom end of R69 being placed near ground potential. The voltage dividing action of R46 and R48 (in series), and R69 reduces the manual gain voltage that can be applied through R43 If the RF GAIN control is fully clockwise, no to the inverting input of U3B. manual gain voltage will be felt at the inverting input of U3B, and the AGC circuitry will exclusively control receiver gain. If the RF GAIN control is rotated counterclockwise, however, a positive voltage (dependent upon the RF GAIN control setting) will be applied to the inverting input of U3B, and reduce receiver gain Since the voltage dividing action of R69, R46, and R48 as described above. reduces the manual gain voltage that can be applied to the inverting input of U3B in the AGC modes of operation, only a limited degree of manual gain control can occur (during AGC operation). The receiver AGC will still be effective as long as the received signal is strong enough to produce a positive AGC voltage at the inverting input of U3B (from U2B) that exceeds the manual gain control voltage at that point as set by the RF GAIN control.

U1C is an electronic switch used to alter the time constant of the peak detector when the HOLD AGC gain mode is selected, and is identical to switches U1A and U1B previously described. If either the NORM AGC or MAN gain mode is selected, a positive voltage from the receiver register applied to board pins N (NAGC) or 12 (MAN), respectively, is routed to control input C of U1C, causing  $C_1$  to be internally connected to  $C_{\,\textbf{C}}$ , which is grounded. This results in R21 being effectively shunted across series circuit R18 and C3, providing the normal fast-attack fast-decayAGC characteristic. In the HOLD AGC gain mode, however, input C of U1C receives no positive input, but instead is held near ground potential. As a result, C, is no longer internally connected to Cc. R21, therefore, no longer shunts series circuit R18 and C3, resulting in a much longer discharge time for  $C_0$  , however, is now internally connected to  $C_0$  , causing the that capacitor. connected end of R72 to be grounded. The effect of R72 is to reduce the output voltage of U2A applied to U2B compensate for the increased input voltage to that amplifier caused by R21 no longer being in shunt with C3. In the HOLD AGC gain mode, only a positive input from Q3 (via R1 and CR7) can cause U1C to revert to its previous state.

Time constant switch U1C is controlled by the hold timer circuit comprised of Darlington pair Q1-Q3 and the associated components. The hold timer uses the audio input voltage from the AM demodulator (board pin 19) as the basis for producing a dc level representing the peak amplitude of the input signal. This is accomplished by applying the (positive) audio input voltage from the AM demodulator through R4 to charge C1. The positive voltage across C1 and R7 turns on Q1 and Q3, resulting in a near-ground potential applied through R1 and CR7 to control input C of U1C. As a consequence, R21 is prevented from shunting C3 (as explained in the previous paragraph), resulting in a long AGC time constant. As the audio input signal drops, C1 discharges causing Q1 and Q3 to begin to shut off. Accordingly, the collector voltage of both transistors begins to rise, but the charging current of C2 through R7 and other shunt impedances apply a counteracting positive bias to the base of Q1, delaying the turn-off time of that transistor and Q2. When the transistors do turn off, the positive voltage at the collectors is applied to control input C of U1C, causing R21 to once again be switched in shunt with C3, producing the fast AGC decay charact-Thus, the hold timer circuit causes the AGC decay time constant to remain long for a fixed period of time (two seconds) after the signal level begins dropping, after which the AGC circuit reverts to its normal fast decay characteristic. By shunting additional capacitance across board pins W and V, the delay time can be increased.

U3A receives AGC voltage at its inverting input (pin 6), amplifies it, and sends it to the gain monitor and signal strength meter circuits. The input to U3A comes from the outputs of both peak detector amplifier U2A and threshold circuit amplifier U2B, provided that either the NORM AGC or HOLD AGC gain modes has been selected. Under weak signal conditions, the input to U3A comes entirely from U2A since U2B produces no output until the received signal level becomes strong enough to reach U2B's threshold. Since the collector of Q8 is near ground potential, R28 and R31 reduce the AGC voltage from the output

Figure 4-6. Simplified Functional Block Diagram of A14U1A and A14U1B

of U2A to the input of U3A. When the received signal becomes strong enough to cause the developed AGC voltage to exceed the threshold level of U2B, the AGC action results in a much slower increase in output voltage from U2A as the received signal level increases. The output of U2B, however, coupled to the inverting input of U3A through CR9, R39, and R36 begins to rise, causing the output of U3A to continue to increase negatively with an increase in received signal strength at approximately the same rate as it rose when the received input signal was below the AGC threshold level. As a result, the signal strength meter readings are not "compressed" for signal levels above the AGC threshold. In the MAN gain mode, a positive input from the receiver register at board pin 12 (MAN) causes Q6 to turn on, Q7 to turn off, Q8 to turn off, and Q9 to turn on. With Q8 off, more voltage from the output of peak detector amplifier U2A is passed to the input of U3A. At the same time, Q9 (now on) shunts the output of U2B (through CR9 and R39), preventing any developed AGC voltage from being applied to the inverting input of U3A. Thus, in the MAN gain mode, only the output of U2A is applied to U3A, as opposed to the NORM AGC and HOLD AGC gain modes where both the output of U2A and U2B are applied to the input of U3A. In any mode, the output of the gain monitor and signal strength circuits is proportional to the received signal strength.

The gain control board has two other features that are not utilized in a standard WJ-8888 Receiver. One of these features is an "AGC dump" circuit comprising Q14, Q15, R50, and R68. During normal operation, a ground potential at board pin D (AGC DUMP) causes Q14 to be cut off, which in turn cuts off Q15. The resulting high collector resistance of Q15 in parallel with time constant capacitor C3 has no appreciable effect on the AGC time constant, and the AGC circuit operates in its normal fashion. If a positive potential (a TTL logic "one" level), however, is applied to board pin D, Q14 and Q15 turn on. The resulting low collector resistance of Q15 rapidly discharges C3, and bring the gain control voltage to zero. The AGC dump feature is typically used in receivers that are remotely controlled in applications where the receiver must tune rapidly from one frequency to another (in such cases, any residual AGC voltage remaining on C3 will momentarily desensitize the receiver until the capacitor has discharged, thus hindering reception at the new tuned frequency).